探索SOC天梯图:构建高效科技架构的实用路线图

- 问答

- 2025-10-01 03:10:09

- 1

探索SOC天梯图:构建高效科技架构的实用路线图

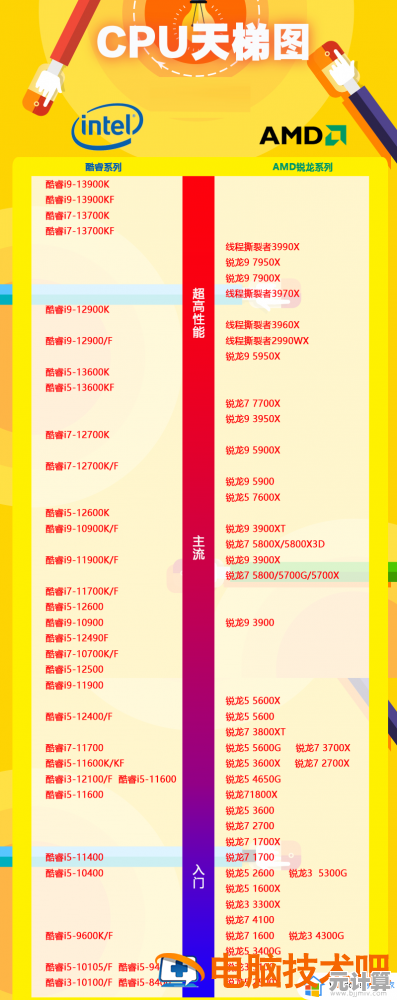

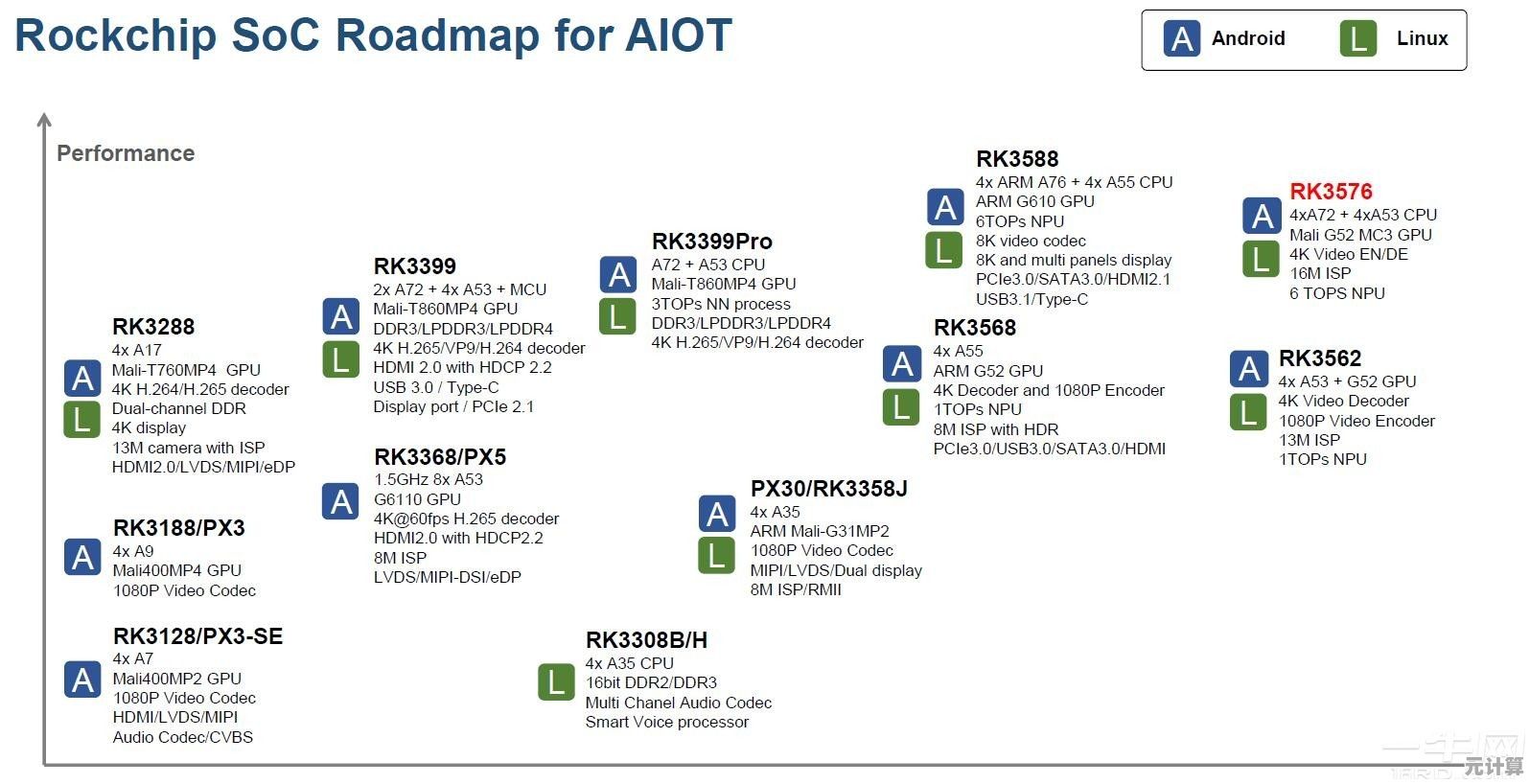

为什么项目总是延期?为什么硬件选型像开盲盒?为什么功耗永远压不住?🤯 这些问题在我十年芯片架构师生涯里反复出现,直到我真正理解了"SOC天梯图"的价值——它不只是性能排名,而是科技产品的生存路线图。

去年我们做智慧城市终端项目时,团队在选主控芯片时吵翻了天,硬件组坚持用某国际大厂旗舰SOC,宣称"性能碾压一切";软件组却看着发热测试数据直摇头,最后妥协用了折中方案,结果现场部署后,夏天高温下设备频繁死机——我们忽略了真实工况下的热功耗墙,只盯着纸面跑分,这个价值三百万的教训让我明白:天梯图必须包含场景化维度。

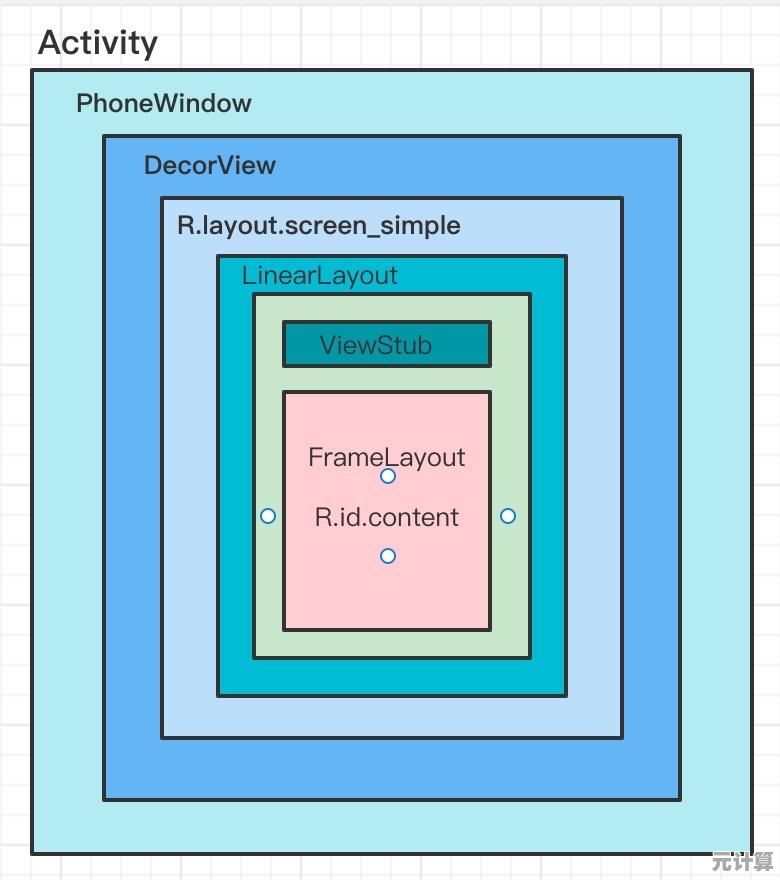

真正的SOC天梯图应该像城市地铁网络图:

- 性能干线(CPU/GPU算力)

- 能效支线(每瓦特效能)

- 专用快车(NPU/ISP等加速器)

- 换乘枢纽(内存带宽与互联)

在工业物联网网关项目里,我们放弃了对标手机的"八核旗舰",转而选择内置双核Cortex-A55+神经处理单元的国产芯片,实测发现其视频分析帧率比某骁龙6系还高30%,功耗却只有1/3——异构计算的价值就在于此:让专用车厢运载专属货物。🚂

构建实用路线图的三块基石:

- 撕掉参数迷信:某项目用安兔兔榜首芯片做AR眼镜,结果GPU浮点性能根本用不满,反而被内存延迟拖垮

- 建立场景沙盘:给智能农机选型时,我们模拟了-30℃冷启动、沙尘暴震动、4G弱网等二十种极端场景

- 预留进化接口:去年设计的充电桩主板,通过预留PCIe插槽成功接入了新的V2X通信模组

最近调试某国产车规级芯片时发现个有趣现象:虽然CPU主频比竞品低15%,但通过总线架构优化,实际多传感器并发处理延迟反而降低40%,这就像城市交通——主干道宽度不如立交枢纽设计重要,高架桥再宽,出口堵死也白搭不是吗?😅

在算力过剩的时代,真正的架构师应该像城市规划者:

- 在算力密度区(如AI推理)建设摩天大楼

- 在实时控制区铺设地铁化专用通道

- 为未来扩展保留城市绿地(可编程逻辑)

上周看到团队新人用天梯图直接选"性能Top3"芯片做手持设备,我默默在他屏幕贴了便签:"请计算200g铝合金外壳在38℃环境下的热传导方程",真正的科技架构,永远在参数与现实的夹缝中生长。

当行业还在争论7nm与5nm的优劣时,我们已用40nm工艺+3D封装做出了满足工规级寿命的传感器——芯片如同乐高,关键不在单块积木的尺寸,而在于咬合方式,毕竟用户要的不是晶体管,而是解决问题的光。

凌晨调试新架构时,示波器波纹突然变得优雅流畅——这种快乐胜过所有天梯排名,或许高效架构的本质,就是让电子在硅晶圆上跳起更美的芭蕾。 💃🕺

本文由丙英叡于2025-10-01发表在笙亿网络策划,如有疑问,请联系我们。

本文链接:http://max.xlisi.cn/wenda/46789.html